|

hsk_libs-dev

163:b63ae088cc97

High Speed Karlsruhe XC878 library collection

|

|

hsk_libs-dev

163:b63ae088cc97

High Speed Karlsruhe XC878 library collection

|

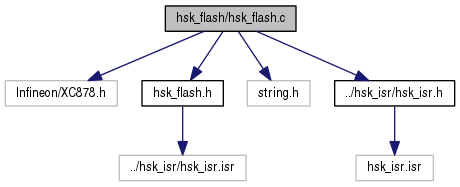

HSK Flash Facility implementation. More...

#include <Infineon/XC878.h>#include "hsk_flash.h"#include <string.h>#include "../hsk_isr/hsk_isr.h"

Macros | |

| #define | MOVCI .db 0xA5 |

| MOVC @(DPTR++),A instruction. More... | |

| #define | DPL dpl |

| DPTR low byte. More... | |

| #define | DPH dph |

| DPTR high byte. More... | |

| #define | VAR_AT(type, name, addr) type __at(addr) name |

| Create variable at a certain address, SDCC version. More... | |

| #define | VAR_ASM(name) _##name |

| Insert global variable address into inline assembler SDCC style. More... | |

| #define | PAGE_RAM 2 |

| XC878-16FF code page that has the Boot ROM and XRAM mapped into it. More... | |

| #define | PAGE_FLASH 0 |

| XC878-16FF code page that has the flash. More... | |

| #define | ADDR_PFLASH 0x0000 |

| XC878-16FF start address of the P-Flash. More... | |

| #define | LEN_PFLASH (60u << 10) |

| XC878-16FF length of the P-Flash. More... | |

| #define | BYTES_PAGE_PFLASH (1 << 9) |

| XC878-16FF the number of bytes in a P-Flash page. More... | |

| #define | BYTES_WORDLINE_PFLASH (1 << 6) |

| XC878-16FF the number of bytes in a P-Flash wordline. More... | |

| #define | ADDR_DFLASH 0xF000 |

| XC878-16FF start address of the D-Flash. More... | |

| #define | LEN_DFLASH (4u << 10) |

| XC878-16FF length of the D-Flash. More... | |

| #define | BYTES_PAGE_DFLASH (1 << 6) |

| XC878-16FF the number of bytes in a D-Flash page. More... | |

| #define | BYTES_WORDLINE_DFLASH (1 << 5) |

| XC878-16FF ld() of the number of bytes in a D-Flash wordline. More... | |

| #define | ADDR_ROM 0xC000 |

| XC878-16FF start address of the Boot ROM. More... | |

| #define | LEN_ROM (8u << 10) |

| XC878-16FF length of the Boot ROM. More... | |

| #define | ADDR_XRAM 0xF000 |

| XC878-16FF start address of the XRAM. More... | |

| #define | LEN_XRAM (3u << 10) |

| XC878-16FF length of the XRAM. More... | |

| #define | BIT_PROG 0 |

| FCON/EECON Program Bit. More... | |

| #define | BIT_ERASE 1 |

| FCON/EECON Erase Bit. More... | |

| #define | BIT_MAS1 2 |

| FCON/EECON Mass Erase Bit. More... | |

| #define | BIT_NVSTR 3 |

| FCON/EECON Non-Volatile Store Bit. More... | |

| #define | BIT_YE 5 |

| FCON/EECON Y-Address Enable Bit. More... | |

| #define | BIT_EEBSY 6 |

| EECON D-Flash Busy Bit. More... | |

| #define | BIT_FTEN 5 |

| FCS Flash Timer Enable Bit. More... | |

| #define | BIT_EEABORT 0 |

| FCS1 D-Flash Program/Erase Abort bit. More... | |

| #define | BIT_OFVAL 0 |

| FTVAL Overflow Value bits. More... | |

| #define | CNT_OFVAL 7 |

| OFVAL bit count. More... | |

| #define | BIT_MODE 7 |

| FTVAL MODE bit. More... | |

| #define | BIT_NMIFLASH 2 |

| NMICON Flash Timer NMI Enable bit. More... | |

| #define | STATE_IDLE 0 |

| The state to use when nothing is to be done. More... | |

| #define | STATE_REQUEST 1 |

| The state to use to kick off a write. More... | |

| #define | STATE_DETECT 10 |

| The state that decides whether a delete or idle is appropriate. More... | |

| #define | STATE_WRITE 20 |

| The state to use when starting to write to the D-Flash. More... | |

| #define | STATE_DELETE 40 |

| The state to use when erasing D-Flash pages. More... | |

| #define | STATE_RESET 60 |

| The state to use when mass erasing the D-Flash. More... | |

| #define | FREE_LATEST 0 |

| The block indicated hsk_flash::latest is available for writing. More... | |

| #define | FREE_BEHIND 1 |

| The block behind the block indicated by hsk_flash::latest is available for writing. More... | |

| #define | FREE_NONE 2 |

| There is no block available for writing. More... | |

Functions | |

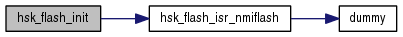

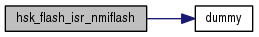

| void | hsk_flash_isr_nmiflash (void) |

| Flash delete/write state machine. More... | |

| ubyte | hsk_flash_init (void *const ptr, const uword size, const ubyte version) |

| Recovers a struct from a previous session and sets everything up for storage of changes. More... | |

| bool | hsk_flash_write (void) |

| Writes the current data to the D-Flash. More... | |

Variables | |

| const ubyte | hsk_flash_dflash [(4u<< 10)] |

| Bytewise access to the D-Flash area. More... | |

| SFR | FCON = 0xD1 |

| P-Flash Control Register. More... | |

| SFR | EECON = 0xD2 |

| D-Flash Control Register. More... | |

| SFR | FCS = 0xD3 |

| Flash Control and Status Register. More... | |

| SFR | FEAL = 0xD4 |

| Flash Error Address Register Low. More... | |

| SFR | FEAH = 0xD5 |

| Flash Error Address Register High. More... | |

| SFR16 | FEALH = 0xD4 |

| Flash Error Address Register Low and High (16 bits). More... | |

| SFR | FTVAL = 0xD6 |

| Flash Timer Value Register. More... | |

| SFR | FCS1 = 0xDD |

| Flash Control and Status Register 1. More... | |

| struct { | |

| ubyte * ptr | |

| The pointer to the data structure to persist. More... | |

| uword size | |

| The size of the data structure to persist. More... | |

| uword wrap | |

| The useable amount of D-Flash. More... | |

| uword oldest | |

| The offset of the oldest data in the D-Flash. More... | |

| uword latest | |

| The offset of the latest data in the D-Flash. More... | |

| ubyte free | |

| This byte indicates where free space can be found in the D-Flash. More... | |

| ubyte ident | |

| The prefix/postfix to identify the data structure in the flash. More... | |

| ubyte state | |

| The current state of the flash ISR state machine. More... | |

| } | hsk_flash |

| Holds the persistence configuration. More... | |

| volatile ubyte * | hsk_flash_flashDptr |

| A pointer to the flash target address. More... | |

| volatile ubyte * | hsk_flash_xdataDptr |

| A pointer to the xdata src address. More... | |

HSK Flash Facility implementation.

This file implements the flash management functions defined in hsk_flash.h.

All registers are in the mapped register are, i.e. RMAP=1 must be set to access them.

Non-blocking flash reading/writing is controlled by a dedicated flash timer. Timings, especially flash writing, are so critical that all the flash delete/write procedures are implemented in a single state machine within hsk_flash_isr_nmiflash(), which is called by a non-maskable interrupt upon timer overflow.

Due to the Byte Order differences between SDCC and C51, the DPL and DPH macros are used to adjust DPTR assignments in inline assembler.

| #define ADDR_DFLASH 0xF000 |

XC878-16FF start address of the D-Flash.

| #define ADDR_PFLASH 0x0000 |

XC878-16FF start address of the P-Flash.

| #define ADDR_ROM 0xC000 |

XC878-16FF start address of the Boot ROM.

| #define ADDR_XRAM 0xF000 |

XC878-16FF start address of the XRAM.

| #define BIT_EEABORT 0 |

FCS1 D-Flash Program/Erase Abort bit.

| #define BIT_EEBSY 6 |

EECON D-Flash Busy Bit.

| #define BIT_ERASE 1 |

FCON/EECON Erase Bit.

| #define BIT_FTEN 5 |

FCS Flash Timer Enable Bit.

| #define BIT_MAS1 2 |

FCON/EECON Mass Erase Bit.

| #define BIT_MODE 7 |

FTVAL MODE bit.

Controls the flash timer speed.

| Mode | Value | Effect |

|---|---|---|

| Program | 0 | 1 count per  (24MHz) clock cycle (24MHz) clock cycle |

| Erase | 1 | 1 count per  clock cycles clock cycles |

| #define BIT_NMIFLASH 2 |

NMICON Flash Timer NMI Enable bit.

| #define BIT_NVSTR 3 |

FCON/EECON Non-Volatile Store Bit.

| #define BIT_OFVAL 0 |

FTVAL Overflow Value bits.

| #define BIT_PROG 0 |

FCON/EECON Program Bit.

| #define BIT_YE 5 |

FCON/EECON Y-Address Enable Bit.

| #define BYTES_PAGE_DFLASH (1 << 6) |

XC878-16FF the number of bytes in a D-Flash page.

| #define BYTES_PAGE_PFLASH (1 << 9) |

XC878-16FF the number of bytes in a P-Flash page.

| #define BYTES_WORDLINE_DFLASH (1 << 5) |

XC878-16FF ld() of the number of bytes in a D-Flash wordline.

| #define BYTES_WORDLINE_PFLASH (1 << 6) |

XC878-16FF the number of bytes in a P-Flash wordline.

| #define CNT_OFVAL 7 |

OFVAL bit count.

| #define DPH dph |

DPTR high byte.

| #define DPL dpl |

DPTR low byte.

| #define FREE_BEHIND 1 |

The block behind the block indicated by hsk_flash::latest is available for writing.

| #define FREE_LATEST 0 |

The block indicated hsk_flash::latest is available for writing.

| #define FREE_NONE 2 |

There is no block available for writing.

| #define LEN_DFLASH (4u << 10) |

XC878-16FF length of the D-Flash.

| #define LEN_PFLASH (60u << 10) |

XC878-16FF length of the P-Flash.

| #define LEN_ROM (8u << 10) |

XC878-16FF length of the Boot ROM.

| #define LEN_XRAM (3u << 10) |

XC878-16FF length of the XRAM.

| #define MOVCI .db 0xA5 |

MOVC @(DPTR++),A instruction.

| #define PAGE_FLASH 0 |

XC878-16FF code page that has the flash.

| #define PAGE_RAM 2 |

XC878-16FF code page that has the Boot ROM and XRAM mapped into it.

| #define STATE_DELETE 40 |

The state to use when erasing D-Flash pages.

| #define STATE_DETECT 10 |

The state that decides whether a delete or idle is appropriate.

| #define STATE_IDLE 0 |

The state to use when nothing is to be done.

| #define STATE_REQUEST 1 |

The state to use to kick off a write.

| #define STATE_RESET 60 |

The state to use when mass erasing the D-Flash.

| #define STATE_WRITE 20 |

The state to use when starting to write to the D-Flash.

| #define VAR_ASM | ( | name | ) | _##name |

Insert global variable address into inline assembler SDCC style.

| #define VAR_AT | ( | type, | |

| name, | |||

| addr | |||

| ) | type __at(addr) name |

Create variable at a certain address, SDCC version.

| ubyte hsk_flash_init | ( | void *const | ptr, |

| const uword | size, | ||

| const ubyte | version | ||

| ) |

Recovers a struct from a previous session and sets everything up for storage of changes.

There are two modes of recovery. After a fresh boot the data can be recovered from flash, if previously stored there. After a simple reset the data can still be found in XRAM and recovery can be sped up.

If recovery fails entirely all members of the struct will be set to 0.

| version | Version number of the persisted data structure, used to prevent initilization with incompatible data |

| ptr | A pointer to the xdata struct/array to persist |

| size | The size of the data structure to persist |

| FLASH_PWR_FIRST | No valid data was recovered |

| FLASH_PWR_RESET | Continue operation after a reset |

| FLASH_PWR_ON | Data restore from the D-Flash succeeded |

|

private |

Flash delete/write state machine.

Every named state is the root of a state machine that performs a specific task.

STATE_REQUEST implements the procedure called "Abort Operation" from the XC878 UM 1.1.

After completing the abort STATE_WRITE is entered.

STATE_DETECT checks whether there is a page that should be deleted.

It either goes into STATE_DELETE or STATE_IDLE.

STATE_WRITE implements the procedure called "Program Operation" from the XC878 UM 1.1.

The next address to write is expected in hsk_flash_flashDptr. The next address to read from XRAM is expected in hsk_flash_xdataDptr.

| bool hsk_flash_write | ( | void | ) |

Writes the current data to the D-Flash.

Ongoing writes are interrupted. Ongoing deletes are interrupted unless there is insufficient space left to write the data.

| 1 | The D-Flash write is on the way |

| 0 | Not enough free D-Flash space to write, try again later |

| SFR EECON = 0xD2 |

D-Flash Control Register.

| SFR FCON = 0xD1 |

P-Flash Control Register.

| SFR FCS = 0xD3 |

Flash Control and Status Register.

| SFR FCS1 = 0xDD |

Flash Control and Status Register 1.

| SFR FEAH = 0xD5 |

Flash Error Address Register High.

| SFR FEAL = 0xD4 |

Flash Error Address Register Low.

| SFR16 FEALH = 0xD4 |

Flash Error Address Register Low and High (16 bits).

| ubyte free |

This byte indicates where free space can be found in the D-Flash.

Available values are:

| SFR FTVAL = 0xD6 |

Flash Timer Value Register.

| hsk_flash |

Holds the persistence configuration.

| const ubyte hsk_flash_dflash[(4u<< 10)] |

Bytewise access to the D-Flash area.

| volatile ubyte* hsk_flash_flashDptr |

A pointer to the flash target address.

Not in a struct for easier inline assembler access.

| volatile ubyte* hsk_flash_xdataDptr |

A pointer to the xdata src address.

Not in a struct for easier inline assembler access.

| ubyte ident |

The prefix/postfix to identify the data structure in the flash.

It consist of the last 6 bits of the version and two alternating bits to make sure the value can neither become 0x00 nor 0xff.

Pre-/postfixing the ident ensures that the data was completely written.

| uword latest |

The offset of the latest data in the D-Flash.

| uword oldest |

The offset of the oldest data in the D-Flash.

| ubyte* ptr |

The pointer to the data structure to persist.

| uword size |

The size of the data structure to persist.

| ubyte state |

The current state of the flash ISR state machine.

| uword wrap |

The useable amount of D-Flash.